**BD**I:

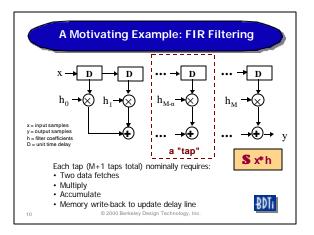

|      |        | TMS32010 Filter Code                                     |      |

|------|--------|----------------------------------------------------------|------|

| LT   | X4     | ;Load T with x(n-4)                                      |      |

| MPY  | H4     | ;P=H4*X4                                                 |      |

| LTD  | Х3     | ;Load T with $x(n-3)$ ; $x(n-4) = x(n-3)$ ;Acc = Acc + P |      |

| MPY  | Н3     | ;P=H3*X3                                                 |      |

| LTD  | X2     |                                                          |      |

| MPY  | H2     |                                                          |      |

| et   | с.     |                                                          |      |

| ♦ Tw | instru | uctions per tap, but requires loop unrolling             |      |

|      |        | © 2000 Berkeley Design Technology, Inc.                  | ₿D1i |

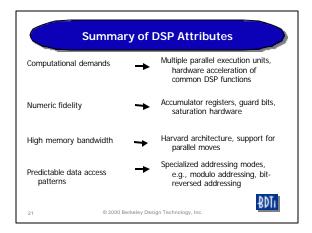

| Summary of DSP Attributes |                 |                                                                                                                  |  |  |  |

|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| Execution-time locality   | +               | Hardware-assisted zero-overhead<br>looping, specialized instruction<br>caches, streamlined interrupt<br>handling |  |  |  |

| MAC-centricity            | +               | Single-cycle multiplier(s) or MAC<br>unit(s), MAC instruction                                                    |  |  |  |

| Streaming data            | →               | No data cache; powerful DMA                                                                                      |  |  |  |

| Real-time constraints     | +               | Few dynamic features, on-chip<br>RAM instead of cache                                                            |  |  |  |

| Standards                 | →               | Rounding, saturation                                                                                             |  |  |  |

| 22 © 2000                 | Berkeley Desigr | Technology, Inc.                                                                                                 |  |  |  |

BDTi

BDTi

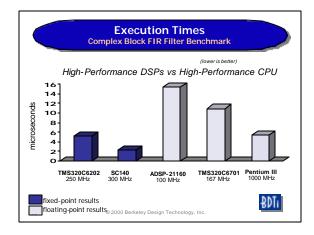

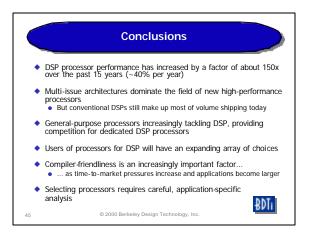

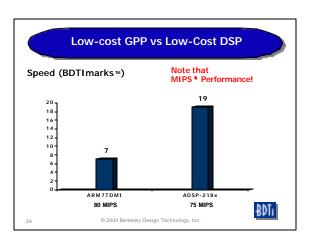

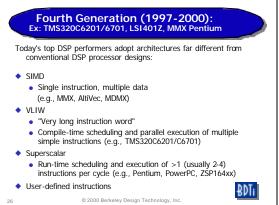

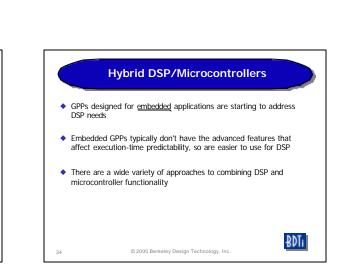

High-Performance GPPs with SIMD

These processors can often execute DSP tasks faster than DSP

© 2000 Berkeley Design Technology, Inc.

processors

• Price

So why do people still use DSPs?

Availability of off-the-shelf DSP software

• DSP-oriented development tools

• DSP-oriented on-chip integration Execution-time predictability is especially problematic with high-performance GPPs

Power consumption